Energy efficient RISC-V processors and accelerators for communications and sensor fusion

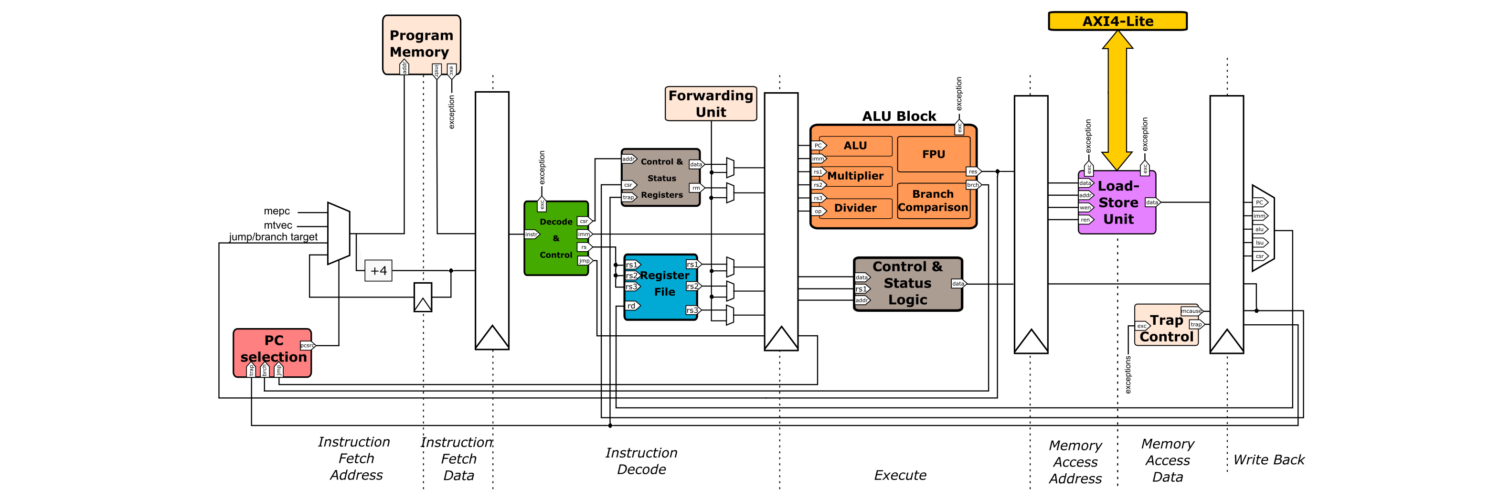

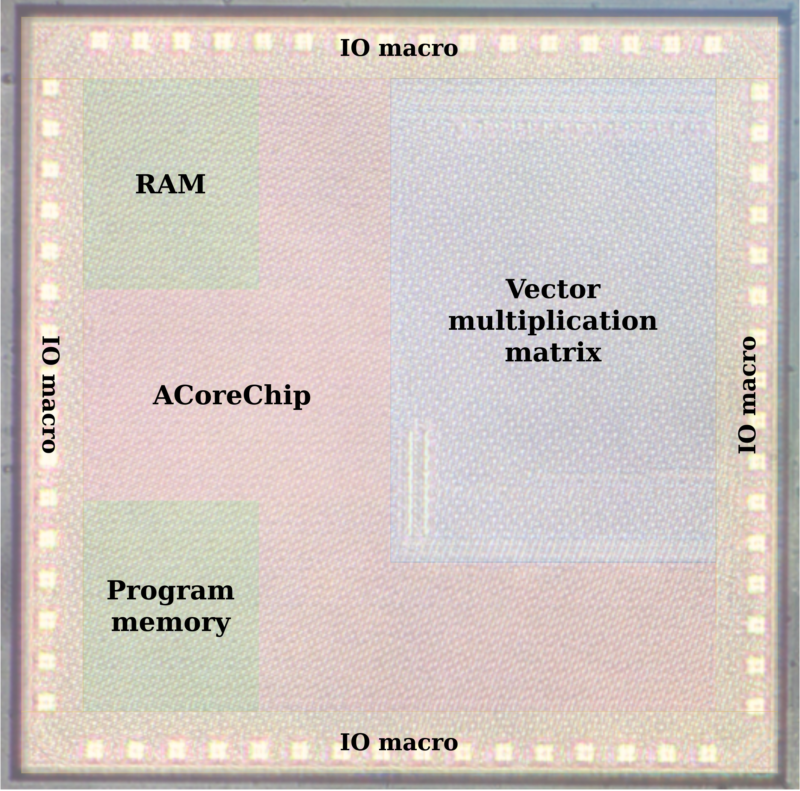

Research of energy-efficient RISC-V processor implementations in Aalto is built around an open-source RISC-V hardware description A-Core ( https://gitlab.com/a-core ) . Starting from instruction-set description, we are gradually adding functionality to the processor, aiming for customized support for 5G and beyond signal processing. We aim for optimal trade-off between energy-efficiency and flexibility by designing customized, reconfigurable accelerators that can be chained to form efficient processing pipelines. These processors can be connected to digital-to-analog converters or transmitter back-ends, or analog-to-digital converters/receiver frontends, to support interfacing for the physical transmit channels of communications. In addition to communications signal processing, we study ways to compensate analog circuit nonidealities with processor-controlled calibration and correction algorithms.

Another topic we study under this field is processor power management in multi-core environment, where we aim to develop performance monitoring of the workload processors and utilize the monitored values with Power Management Unit, a dedicated RISC-V core running advanced power management software. Eventually, this will result in load-aware power management for a multi-core communications processor, improving the energy-efficiency of the whole system.

Third theme under this field is low-power sensor control in extremely low temperatures. We are developing processor cores that can operate in sub-kelvin temperatures to monitor and control the operation of cryostats and to avoid excess wiring that is challenging to implement while maintaining the low temperature. This implementation environment is extremely challenging due to stringent power consumption limits to avoid heating the system.

As a whole, our processor research serves well our educational objectives, since it combines, in an interesting way, programming and microelectronics design at the very core of software-hardware interface.